Convert Input Vector of Bits to Integer

This example shows how to use the Bits to Word block in a Simulink® Model that converts vector of bits to an unsigned integer. You also generate HDL code for the model.

Simulate Model

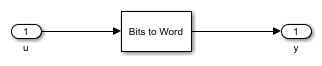

Load and open the hdlcoder_bits_to_word model. The DUT subsystem contains Bits to Word block that converts a vector of bits to an unsigned integer.

load_system("hdlcoder_bits_to_word"); open_system("hdlcoder_bits_to_word/DUT");

Simulate the hdlcoder_bits_to_word model. The input is a vector of length 5. The block treats first element of the input vector as the least significant bit (LSB) of the output. The output of the block is an unsigned integer with the ufix5 type.

sim('hdlcoder_bits_to_word');

Generate HDL code

You can generate the HDL code for a model by using HDL Coder™. To generate HDL code for DUT subsystem, run this makehdl command:

makehdl("hdlcoder_bits_to_word/DUT")