Descrambling with Gold Sequence Generator

This example shows how to use the LTE Gold Sequence Generator block to implement an LTE descrambler.

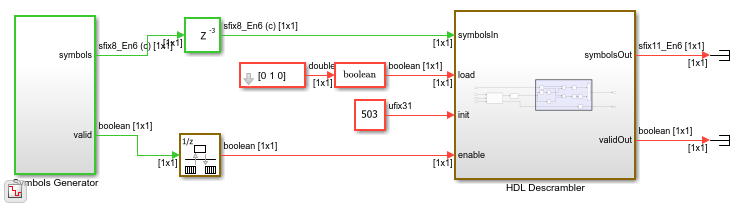

The example model generates random I-Q pairs, multiplies the I and Q components with a generated Gold sequence, and interleaves the I and Q into a single data stream.

You can generate HDL from the HDL Descrambler subsystem.

The LTE Gold Sequence Generator block has no block parameters. It is configured to match the polynomial and shift length required by LTE standard TS 36.212. You must initialize the sequence with a 31-bit value on the init port, and load the value into the block by setting the load signal to 1 for one cycle. The enable signal generates the Gold sequence values. The output valid signal indicates when the output is available.

You can add data logging on the signals and use the Logic Analyzer to view the waveforms.

To generate and check the HDL code referenced in this example, you must have an HDL Coder™ license.

To generate the HDL code, use the following command:

makehdl('ltehdlGoldDescramblerModel/HDL Descrambler')

To generate a test bench, use the following command:

makehdltb('ltehdlGoldDescramblerModel/HDL Descrambler')