Generazione di codice HDL

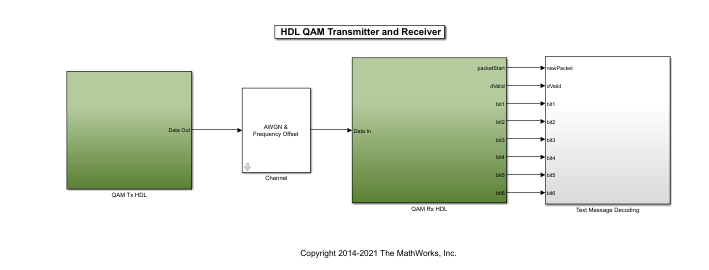

È possibile utilizzare le feature HDL Coder™ per implementare progetti di sistemi di comunicazione su FPGA o ASIC. È possibile generare codice VHDL® e Verilog® sintetizzabile e portabile nonché banchi di prova VHDL e Verilog per simulare, testare e verificare rapidamente il codice generato. È possibile generare codice da progetti Simulink o MATLAB. Questo supporto comprende la correzione e il rilevamento degli errori, la modulazione, i filtri, le operazioni matematiche e di segnale e altri algoritmi ottimizzati per l'utilizzo delle risorse e le prestazioni, come il blocco NCO (DSP HDL Toolbox). Per un esempio di base su come generare codice HDL, vedere Programmable FIR Filter for FPGA.

Per eseguire il debug dei progetti in Simulink o MATLAB, utilizzare il visualizzatore di forme d'onda Logic Analyzer.

Argomenti

- Find Blocks That Support HDL Code Generation

Filter for blocks that support HDL code generation in the Simulink library browser and in documentation.

- Wireless Communications Design for ASICs, FPGAs, and SoCs

Design wireless communication algorithms for hardware by using Wireless HDL Toolbox™ blocks.

Strumenti di visualizzazione Simulink

| Logic Analyzer | Visualize, measure, and analyze transitions and states over time |