Optimization Basics

Optimize your design for a target FPGA or SoC device by applying optimizations such as hierarchy flattening, delay balancing, or feedback loop highlighting. Applying base optimizations helps to generate more hardware-efficient HDL code and properly simulate the generated code.

Topics

- Introduction to Optimizations in HDL Coder

Learn about speed and area optimizations and how to optimize your design.

- Enabling Optimizations in HDL Coder

Learn the settings that directly impact the speed and area of the generated HDL code.

- Find Feedback Loops

Highlight feedback loops that are inhibiting optimizations.

- Hierarchy Flattening

Flatten subsystem hierarchy to enable more extensive area and speed optimization.

- Optimization with Constrained Overclocking

Optimization with constrained overclocking and how it works.

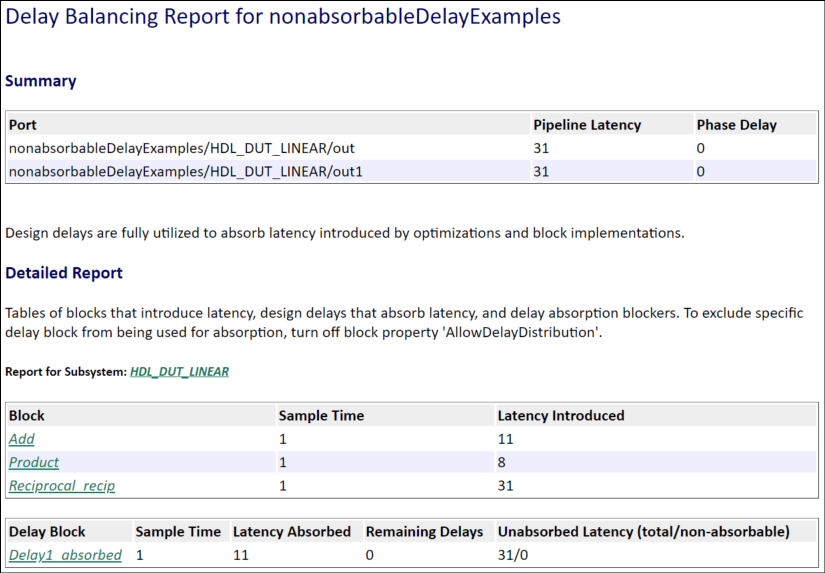

- Understand Delay Balancing in HDL Coder

Insert matching delays along data paths.

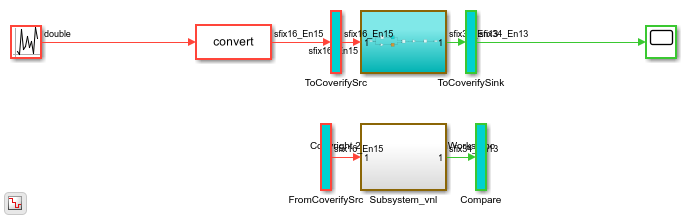

- Use Delay Absorption While Modeling with Latency

Model with latency to absorb design delays and prevent a timing mismatch between the original and generated model.

- Generated Model and Validation Model

The generated model is a model created during HDL code generation that shows the HDL implementation architecture and includes latency.

- Remove Redundant Logic and Unused Blocks in Generated HDL Code

Improve readability of generated HDL code and optimize area usage.

- Optimize Unconnected Ports in HDL Code for Simulink Models

Optimize unused ports in generated HDL code in combination with redundant logic deletion.

- Simplify Constant Operations and Reduce Design Complexity in HDL Coder

Area and timing optimizations that simplify constants and optimize mathematical operations.

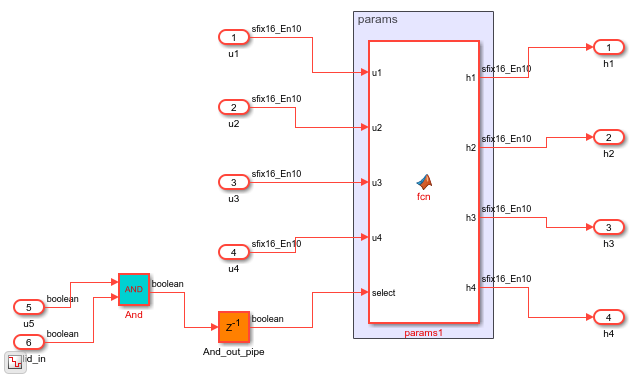

- Enable-Based Multicycle Path Constraints

Generate enable-based constraints for synthesis tools to meet timing requirements of multicycle paths in single clock mode.

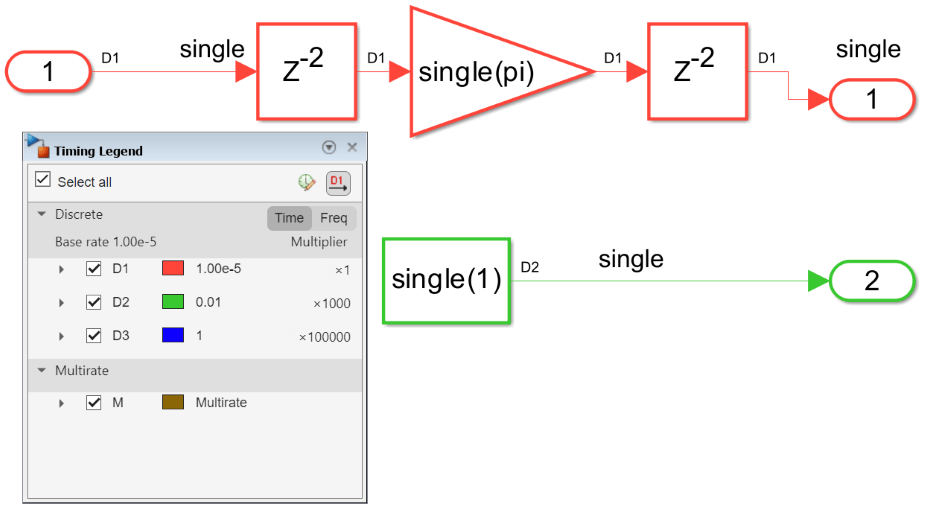

- Generate Multicycle Path Constraints for Multirate Models

Generate Multicycle Path Constraints for Different Rates and Phases.

- Choose Between Multicycle Path Constraints and Clock-Rate Pipelining

Decide whether to use multicycle path constraints (MCP) or clock-rate pipelining (CRP) to meet timing requirement.

- Iteratively Meet Timing Requirements Using Multicycle Path Constraints for Cadence Genus

Use multicycle path constraints with HDL Workflow Advisor and Cadence Genus synthesis tools to meet the timing requirements for ASIC devices.

Troubleshooting

Resolve Delays Not Absorbed During Delay Balancing

Troubleshoot extra latency not absorbed during HDL code generation.