Uso di Simulink Design Verifier per la verifica sistematica dei modelli

Gli ingegneri di controllo nei settori automotive e aerospaziale devono garantire che gli algoritmi di controllo sottostanti abbiano il comportamento desiderato durante tutto il ciclo di vita operativo.

Simulink® Design Verifier™ consente di eseguire una verifica sistematica dei modelli per identificare errori di progettazione nascosti, dimostrare proprietà e generare casi di test per i test funzionali. Simulink Design Verifier utilizza metodi di verifica formali per testare la correttezza della progettazione e aumentare la fiducia nel modello di progettazione da cui viene generato il codice di produzione. Ad esempio, gli ingegneri possono eseguire la verifica e la validazione durante il ciclo di vita dello sviluppo per garantire che:

Il sistema di gestione del motore non provochi comportamenti indesiderati quali accelerazioni non intenzionali o spegnimento del motore durante il funzionamento.

Le applicazioni del sistema avanzato di assistenza alla guida (ADAS) che controllano i freni e lo sterzo funzionino bene in tutte le condizioni.

I sistemi autopilota rispondano correttamente a tutte le possibili condizioni di volo e a tutti gli input.

I sistemi di controllo di volo siano stabili e reattivi per prevenire guasti catastrofici durante il volo.

Un progettista di modelli e un ingegnere di test utilizzano Simulink Design Verifier nella fase di sviluppo del modello in evoluzione per raggiungere la verifica e la validazione.

Funzionalità di Simulink Design Verifier

Simulink Design Verifier offre feature quali:

| Funzionalità | Descrizione |

|---|---|

| Analisi dei requisiti funzionali |

Per maggiori informazioni, vedere Use Specification Models for Requirements-Based Testing. |

| Generazione dei test |

Per maggiori informazioni, vedere Workflow for Test Generation. |

| Rilevamento degli errori di progettazione |

Per maggiori informazioni, vedere What Is Design Error Detection? |

| Dimostrazione delle proprietà |

Per maggiori informazioni, vedere Prove Model Properties |

| Analisi incrementale, filtraggio e giustificazione |

|

Analisi del codice generato |

|

Certificazione o conformità | Conseguire la conformità agli standard industriali quali ISO 26262 per il settore automotive o DO-178C per quello aerospaziale utilizzando gli artefatti generati. |

Come si utilizza Simulink Design Verifier

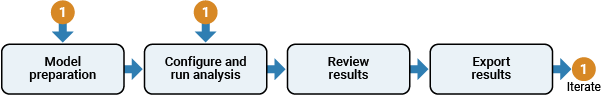

L'utilizzo di Simulink Design Verifier comporta le seguenti fasi principali.

Preparazione del modello: preparare il modello per l'analisi.

Selezionare la modalità di analisi, ad esempio generazione di casi di test, rilevamento di errori di progettazione o analisi di verifica delle proprietà.

Configurare i parametri di analisi e verificare la compatibilità del modello con l'analisi. Per maggiori informazioni, vedere Analyze Model and Interpret Results.

Configurare le impostazioni del modello ed eseguire l'analisi: specificare le impostazioni del modello ed eseguire l'analisi pertinente alle proprie esigenze.

Selezionare il tempo massimo di analisi, la modalità di coverage, la modalità di errore di runtime, la strategia e altri parametri di configurazione per l'analisi.

Eseguire l'analisi.

Revisionare i risultati: visualizzare i risultati generati.

Esaminare i risultati del modello evidenziato da Simulink Design Verifier al termine dell'analisi.

Revisionare lo stato degli obiettivi e definire le azioni di follow-up.

Generare il report di analisi.

Esportazione dei risultati: utilizzare le informazioni ottenute dai risultati per perfezionare il modello o l'impostazione dell'analisi.

Creare un harness per la simulazione.

Esportare i casi di test in Simulink Test™.

Per maggiori informazioni, vedere Analyze Model and Interpret Results.

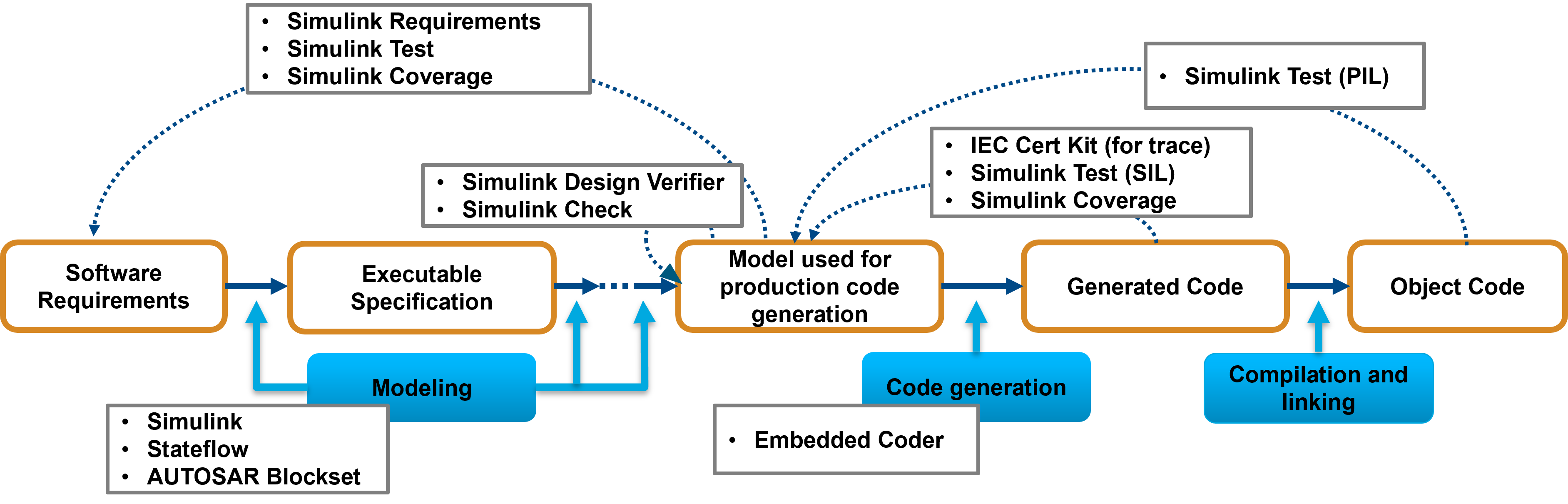

Simulink Design Verifier nella progettazione Model-Based

Questa figura illustra le capacità di Simulink Design Verifier nelle varie fasi dei workflow di verifica e validazione.

Con Simulink Design Verifier, è possibile:

Identificare errori di progettazione nascosti, come overflow di interi o divisioni per zero e generare controesempi per eseguire il debug di funzionalità non intenzionali. È inoltre possibile giustificare o escludere oggetti del modello dall'analisi.

Verificare il modello rispetto ai requisiti utilizzando Requirements Toolbox™.

Integrare la coverage del modello (Simulink Coverage) generando casi di test che soddisfano gli obiettivi di coverage del modello.

Eseguire l'analisi della coverage del codice (Embedded Coder) generando casi di test per il codice generato da Embedded Coder®.

Estendere i casi di test esistenti e integrare la coverage mancante.

Integrare i casi di test con Simulink Test per eseguire test baseline e di equivalenza.

Supportare gli standard industriali tramite IEC Certification Kit (for IEC 61508 and ISO 26262) e DO Qualification Kit (for DO-178).

Simulink Design Verifier supporta inoltre la conformità agli standard industriali tramite IEC Certification Kit (for IEC 61508 and ISO 26262) e DO Qualification Kit (for DO-178).