Speed and Area Optimization

Improvements through resource sharing, streaming, pipelining, RAM mapping

For your target hardware, generate HDL code from a MATLAB® function that meets timing and area requirements by using speed and area optimizations. Area optimizations reduce resource usage of your design. Speed optimizations improve the timing of your design on the target FPGA so that your design runs at higher frequencies by optimizing the critical path. To learn more about each type of optimization in HDL Coder™, see Speed and Area Optimizations in HDL Coder.

Functions

coder.hdl.loopspec | Unroll or stream loops in generated HDL and High-Level Synthesis (HLS) code |

coder.hdl.pipeline | Insert pipeline registers at output of MATLAB expression |

coder.hdl.ramconfig | Specify RAM mapping configuration for persistent array variables (Since R2023b) |

hdl.npufun | Apply neighborhood processing and element-wise operations to incoming image or matrix for frame-to-sample conversion (Since R2022b) |

hdl.iteratorfun | Apply iterative operation to an incoming image or matrix for frame-to-sample conversion (Since R2022b) |

Topics

Optimization Basics

- Speed and Area Optimizations in HDL Coder

Learn about various speed and area optimizations and how to optimize your design. - Specify the Clock Enable Rate

Configure clock enable to run at design base rate or input data rate. - Minimize Clock Enables

Generate code for registers without clock enables. - Constant Multiplier Optimization

What is Constant multiplier optimization and how to specify this optimization.

Area Optimization

- Apply RAM Mapping to Optimize Area

Map elements to RAM to optimize area on your target hardware. - Manage How HDL Coder Maps RAM

Learn how HDL Coder settings affect RAM mapping. - Map Persistent Arrays and dsp.Delay Objects to RAM

Map persistent arrays anddsp.Delayobjects to RAM on hardware to reduce the area used on your target device. - Map Matrices to ROM

Map matrices to implement ROM in MATLAB and Simulink. - Map Matrices to Block RAMs to Reduce Area

This example shows how to use the RAM mapping optimization in HDL Coder™ to map persistent matrix variables to block RAMs in hardware. - Loop Streaming to Reduce Area

This example shows how to use the design-level loop streaming optimization in HDL Coder™ to optimize area.

Speed Optimization

- Pipelining MATLAB Code

Pipelining helps achieve a higher maximum clock rate by inserting registers at strategic points in the hardware to break the critical path. - Pipeline MATLAB Expressions

Insert registers at output of MATLAB expression. - Optimize MATLAB Loops

Optimize loops for area or speed. - Distributed Pipelining

Distributed pipelining definition, benefits, and costs. - Clock-Rate Pipelining

Pipeline registers insertion at the faster clock rate instead of the slower data rate.

I/O Optimization

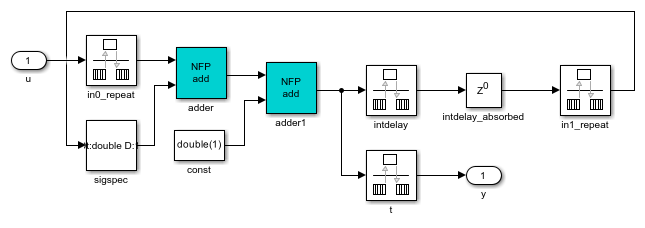

- Use Neighborhood, Reduction, and Iterator Patterns with a Frame-Based Model or Function for HDL Code Generation

Generate HDL code from a frame-based design that models neighborhood, reduction, and iterator patterns.