Revisione dei risultati di analisi di rilevamento degli errori di progettazione

Al termine dell'analisi di rilevamento degli errori di progettazione:

Simulink® Design Verifier™ evidenzia il modello con i risultati di analisi.

Si apre la finestra Results Summary (Riepilogo risultati) di Simulink Design Verifier che mostra un riepilogo dell'analisi.

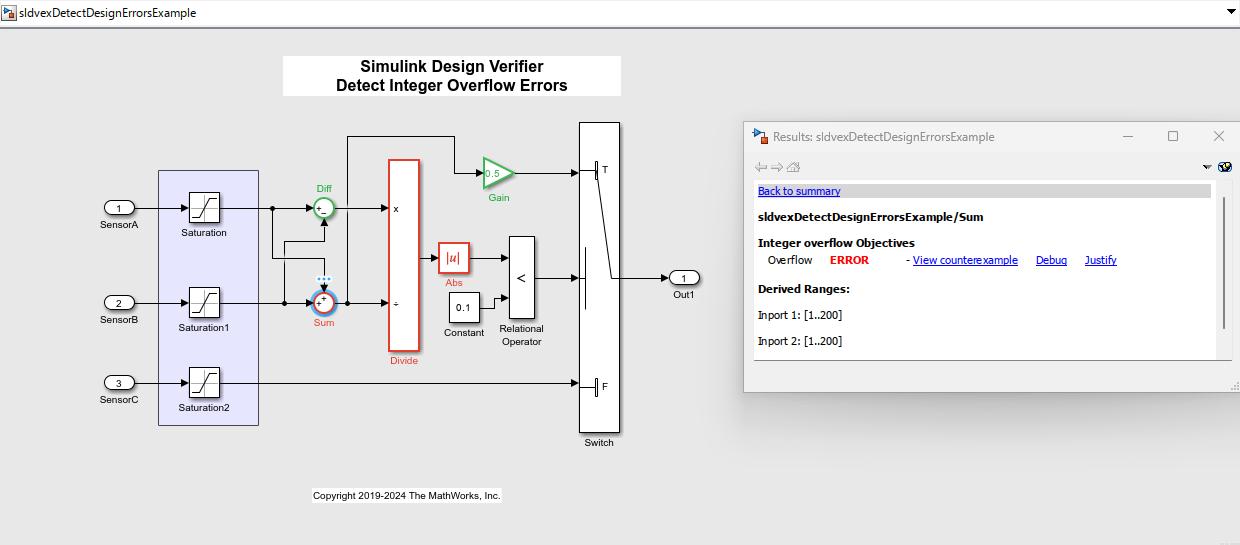

Evidenziazione dei risultati dell'analisi sul modello

Una volta completata l'analisi di rilevamento degli errori di progettazione, i risultati vengono evidenziati automaticamente nel modello sldvexDetectDesignErrorsExample.

1. Selezionare il blocco Sum. La finestra Results (Risultati) mostra gli obiettivi di overflow di interi del blocco Sum.

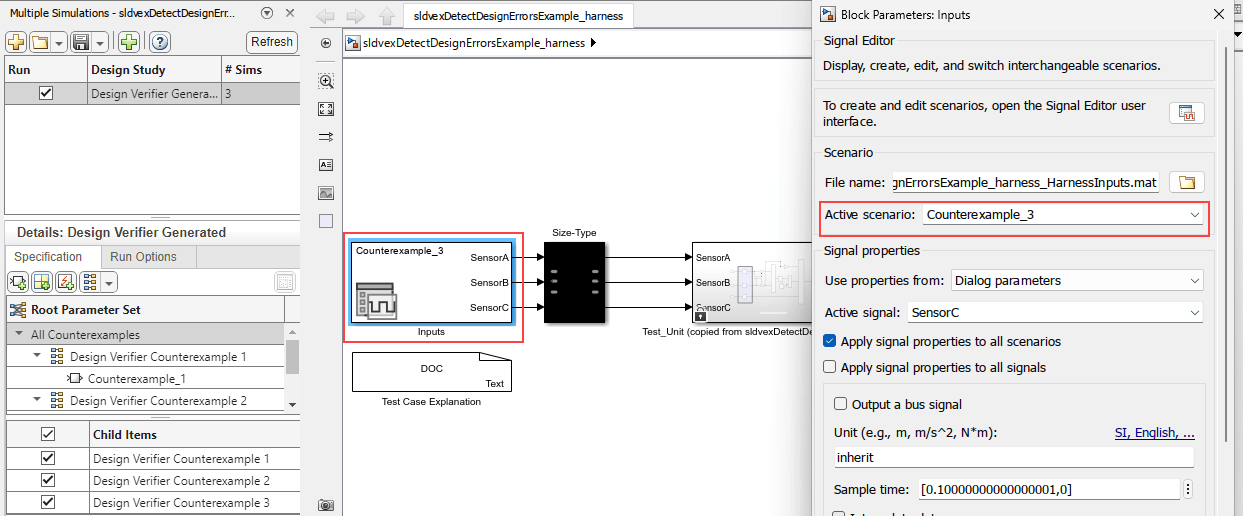

2. Per eseguire il debug dell'errore di overflow di interi, fare clic su View counterexample (Visualizza controesempio). Si apre il modello harness sldvexDetectDesignErrorsExample_harness e la finestra di dialogo Block Parameters (Parametri del blocco) Inputs.

3. Nella finestra di dialogo Block Parameters (Parametri del blocco), dall'elenco Active scenario (Scenario attivo), selezionare Counterexample_3. Fare clic su Apply (Applica).

Il blocco Input nel modello harness indica Counterexample_3 come scenario attivo.

4. Fare doppio clic sul blocco Inputs per aprire la finestra di dialogo Block Parameters (Parametri del blocco).

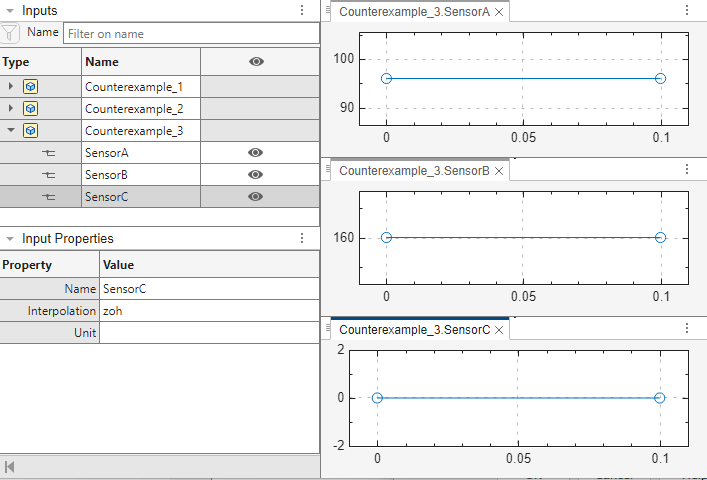

5. Nella finestra di dialogo Block Parameters (Parametri del blocco), fare clic sul pulsante Open Signal Editor (Apri Editor dei segnali) da ![]() per visualizzare lo scenario.

per visualizzare lo scenario.

Quando il valore di input di CounterExample_3.SensorA è 96 e il valore di input di CounterExample_3.SensorB è 160, l'output del blocco Sum va in overflow. Il tipo di dato dell'accumulatore del blocco Sum è impostato su un tipo non corretto uint8, che provoca errori di overflow ed errori di divisione per zero sul blocco Divide a valle.

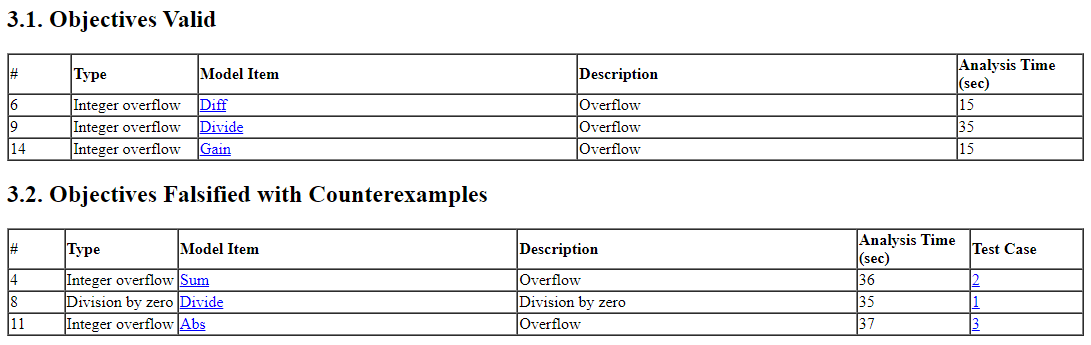

Report di analisi del rilevamento degli errori di progettazione

Per visualizzare il Report di analisi del rilevamento degli errori di progettazione HTML, nella finestra Results Summary (Riepilogo dei risultati), fare clic su HTML. Il report HTML si apre nell'Editor di MATLAB®. La sezione Obiettivi di rilevamento degli errori di progettazione del report elenca gli obiettivi di ciascun elemento del modello e la relativa descrizione.

Il report dell'analisi mostra che tre obiettivi sono validi e tre obiettivi sono falsificati con controesempi.