Rilevamento di errori di progettazione comuni

Prima di eseguire l'analisi di rilevamento degli errori di progettazione, verificare la presenza di difetti nel modello utilizzando Defect checker. Defect checker riporta il numero di difetti presenti nel modello durante tutta la fase di sviluppo per errori di progettazione comuni e critici quali divisione per zero, overflow di interi, logica morta e array fuori limite.

Utilizzo di Defect checker

Aprire il modello sldvexDetectDesignErrorsExample. nella scheda Design Verifier, verificare che Defect Checker sia selezionato.

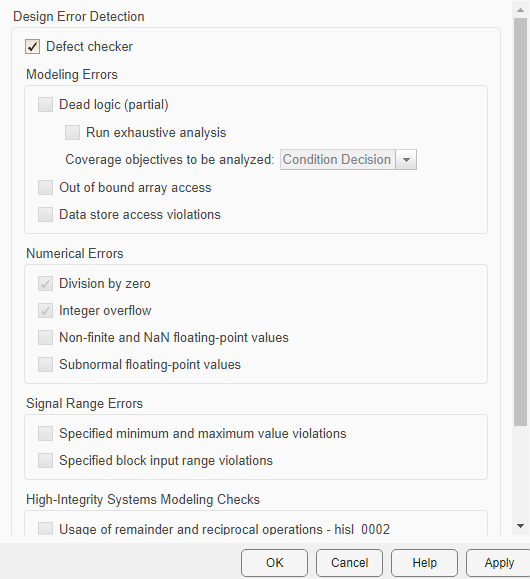

In alternativa, nella finestra di dialogo Configuration Parameters (Parametri di configurazione), nel riquadro Design Verifier > Design Error Detection (Rilevamento degli errori di progettazione), verificare che Defect Checker sia selezionato.

Esecuzione dell'analisi

Per rilevare errori di progettazione comuni utilizzando Defect Checker, nella scheda Design Verifier, fare clic su Detect Design Errors (Rileva errori di progettazione).

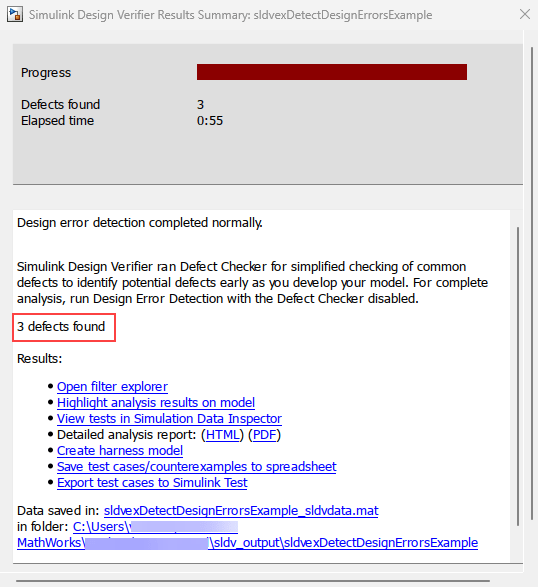

Simulink Design Verifier analizza il modello sldvexDetectDesignErrorsExample per individuare eventuali difetti e visualizza il numero di difetti rilevati durante l'analisi nella finestra Results Summary (Riepilogo risultati).

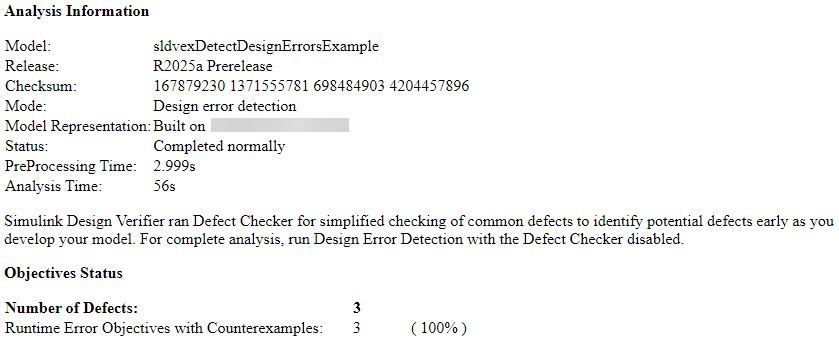

I risultati di analisi indicano che il modello presenta tre difetti. È possibile visualizzare il report di analisi dettagliato facendo clic su HTML o PDF nella finestra Results Summary (Riepilogo dei risultati). Il report mostra gli obiettivi degli errori di runtime con i controesempi per i blocchi Sum, Divide e Abs. Per maggiori informazioni sullo stato dell'obiettivo, vedere Review Results from Analysis Report.

Il capitolo Analysis Information (Informazioni sull'analisi) nel report indica che l'analisi Defect checker ha eseguito un controllo semplificato dei difetti comuni.