Design and Simulate an Algorithm Using Vitis Model Composer | Getting Started with the Avnet ZUBoard, Part 2

From the series: Getting Started with the Avnet ZUBoard

Become familiar with the project workflow and simulate a FIR filter using MATLAB®, Simulink®, and AMD-Xilinx® Vitis™ Model Composer. Change system conditions and view simulation results. When simulation is complete, create a final IP block.

Published: 26 Aug 2022

Hello there. How would you like to design and simulate a filter using Vitis Model Composer for AMD-Xilinx? I'm John Pitrus from MathWorks. This is a four-part video series that covers getting started with the Avnet ZUBoard Development Kit.

In the last video, I showed you how to set up the project. Today, I'm going to discuss designing an algorithm and simulating on your PC. Next, I'll talk about how to elaborate the design for a specific FPGA device and hardware. And lastly, for part four, I'll show you how to create the final bitstream file to program the FPGA.

The main package we'll use today is called Vitis Model Composer. This is an environment for designing algorithms and performing architectural trade-offs. Once you're all done and satisfied with performance, Vitis Model Composer will generate code automatically for your design and perform verification. If you want to learn more, you can go to this website page to read about features and capabilities and try some of the tutorials and examples on your own.

So let's go ahead to the Vitis Model Composer shortcut here and start up the program. Here is our main window. On the left, you can see folder and file hierarchy. In the middle is our Command Window and Editor, and on the right is our Workspace. So here's our design file for today. We'll open that up.

Before we get into the filter design details, let me show you Library Browser. This is all of the design blocks you can use and integrate within your design. So for example, if you're interested in filters, there are 113 different blocks to choose from. On the bottom here, you can see the Xilinx-specific blocks for both HDL, HLS, and other functions. So it's a very rich design environment with a lot of graphs and blocks to use for your design.

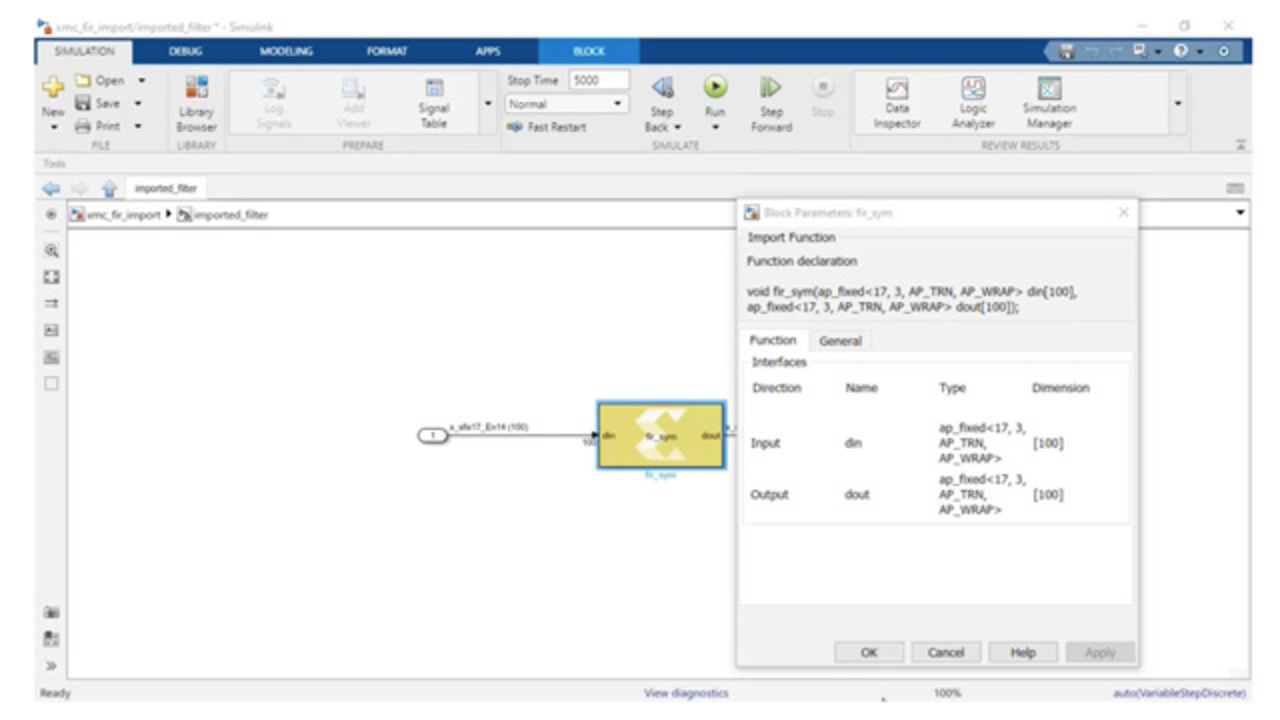

Back to our FIR filter design, there's a source coming in shaped into a data matrix converted here. Here's our filter design for today's design, it's a 103 tap filter. Convert it over again and feed it a spectrum analyzer output. So let's go ahead and run that. You can see the frequency response there. It's a little band pass filter, as shown in the output on the top right.

One more thing I wanted to show you is the Model Composer hub. We know what our target hardware is, so it's the Zync UltraScale MPSoC 1cg FPGA device, so we have to specify that here under Target. In Settings, we'll want to make sure we specify the IP Catalog block for the output type.

And then in the Generate screen, here's the location where the design files will be placed by Vitis Model Composer. And we will go ahead and hit Generate. And it looks like Vitis Model Composer ran OK. We get a status report here of resources used, performance estimates, latency, interfaces, and where all the I/O have been placed.

Let's review what I've discussed. In this video, I showed you how to design an algorithm and simulate it on your PC and then run Vitis Model Composer to produce an IP catalog output. In the next video, I'll talk about how to elaborate the design and bring it into the design environment for synthesis place and route. Thank you for watching.