Revisione dei risultati dell'analisi della generazione dei test

Rivedere i risultati dell'analisi dopo che Simulink® Design Verifier™ ha completato l'analisi in uno dei seguenti modi:

Evidenziare i risultati nel modello.

Visualizzare un report di analisi.

Revisione dei risultati dell'analisi della generazione dei test

Completare le prime due fasi di questo tutorial per eseguire l'analisi della generazione dei test, quindi rivedere i risultati.

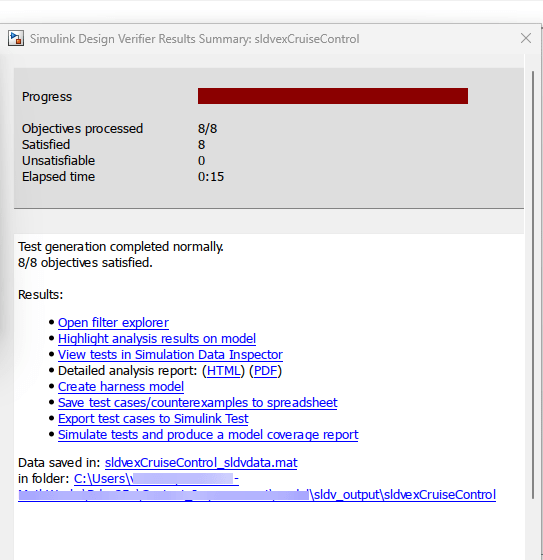

Al termine dell'analisi, la finestra Results Summary (Riepilogo dei risultati) visualizza le opzioni per rivedere i risultati. Per qualsiasi analisi Simulink Design Verifier, è possibile eseguire attività dalla finestra Results Summary (Riepilogo dei risultati).

In alternativa, nella scheda Design Verifier (Verifica del progetto), fare clic su Results Summary (Riepilogo dei risultati) nella sezione Review Results (Revisione dei risultati) per visualizzare i risultati.

Finché il modello rimane aperto, è possibile visualizzare i risultati dell'analisi Simulink Design Verifier più recente nella finestra Results Summary (Riepilogo dei risultati).

Evidenziazione dei risultati dell'analisi sul modello

Durante l'analisi, Simulink Design Verifier evidenzia automaticamente gli oggetti del modello quando lo stato degli obiettivi viene aggiornato.

Per evidenziare i risultati dell'analisi sul modello sldvexCruiseControl:

1. Nella finestra Results Summary (Riepilogo dei risultati) dell'analisi sldvexCruiseControl, fare clic su Highlight analysis results on model (Evidenzia i risultati dell'analisi sul modello).

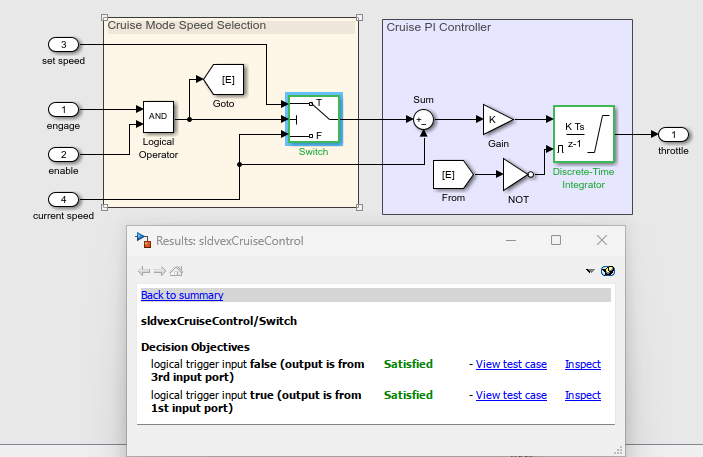

Il blocco Switch è evidenziato in verde, a indicare che presenta i casi di test che soddisfano i relativi obiettivi di test.

2. Per impostazione predefinita, la finestra Results (Risultati) di Simulink Design Verifier è sempre la finestra visibile in primo piano. Per consentire alla finestra di spostarsi dietro ad altre finestre, fare clic con il tasto destro del mouse sulla finestra e deselezionare Always on top (Sempre in primo piano). Quando si fa clic sugli oggetti nel modello, questa finestra cambia per visualizzare i risultati dettagliati dell'analisi per quell'oggetto.

3. Fare clic sul blocco Switch evidenziato.

Il riepilogo mostra che tutti gli obiettivi del blocco Switch sono stati soddisfatti. In modo analogo, fare clic sul blocco Discrete-Time Integrator evidenziato per visualizzare i risultati dell'analisi per questo blocco nella finestra Results (Risultati) di Simulink Design Verifier. Per maggiori informazioni sui risultati dell'analisi evidenziati su un modello, vedere Highlight Results on the Model.

Revisione del report di analisi dettagliato

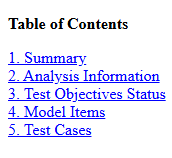

Nella finestra Results Summary (Riepilogo dei risultati) di Simulink Design Verifier, accanto a Detailed analysis report (Report di analisi dettagliato), fare clic su HTML. Il report HTML si apre nell'Editor di MATLAB®.

Il report include questo indice dei contenuti.

Il capitolo Summary (Riepilogo) elenca le informazioni relative al modello e allo stato degli obiettivi, soddisfatti o meno.

Il capitolo Analysis Information (Informazioni sull'analisi) fornisce informazioni su quanto segue:

Il modello analizzato.

Le opzioni specificate per l'analisi.

Le approssimazioni eseguite dal software durante l'analisi.

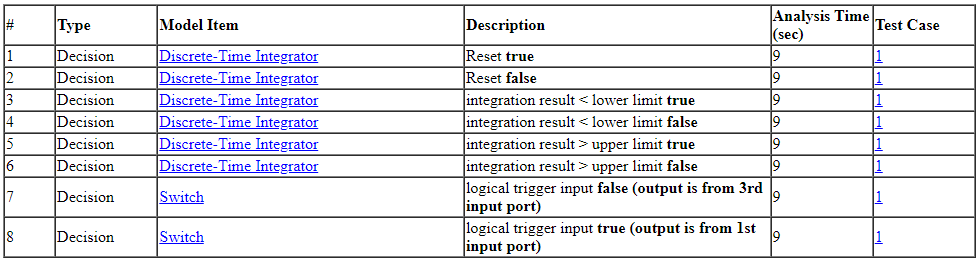

Il capitolo Test Objectives Status (Stato degli obiettivi) del test nel report HTML include descrizioni dettagliate degli obiettivi soddisfatti per ogni elemento del modello e per ogni caso di test generato.

Nella colonna Test Case (Caso di testo) della tabella, fare clic su 1 per visualizzare la sezione Caso di test 1.

La sezione Test Objective Status (Stato dell'obiettivo del test) fornisce dettagli su un caso di test generato dall'analisi per conseguire un obiettivo nel modello. Per maggiori informazioni sui report HTML, vedere Review Results.

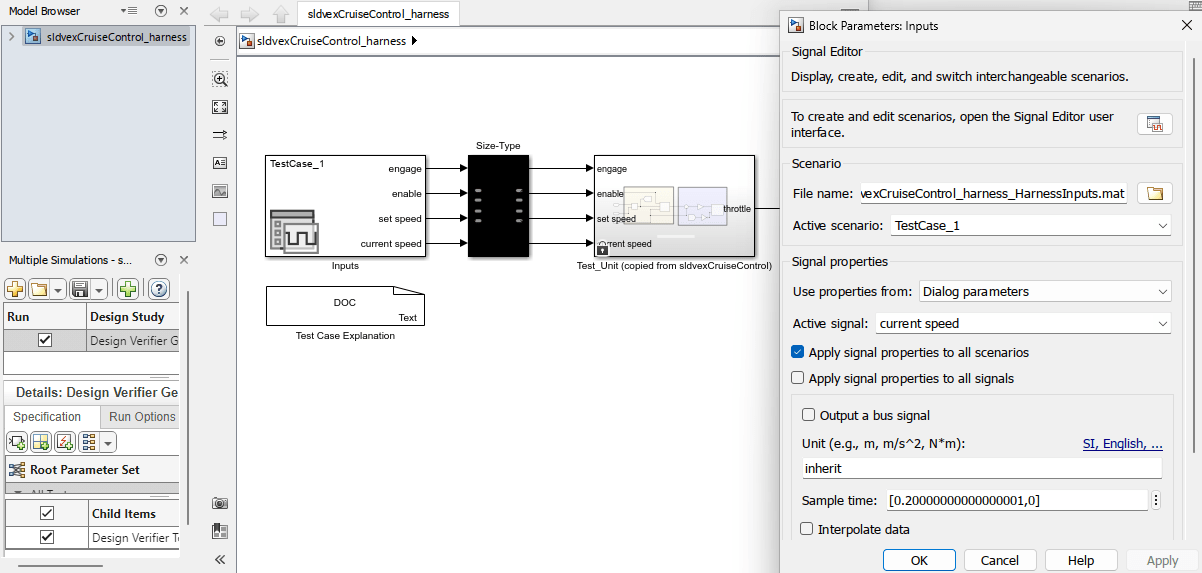

Revisione del modello harness

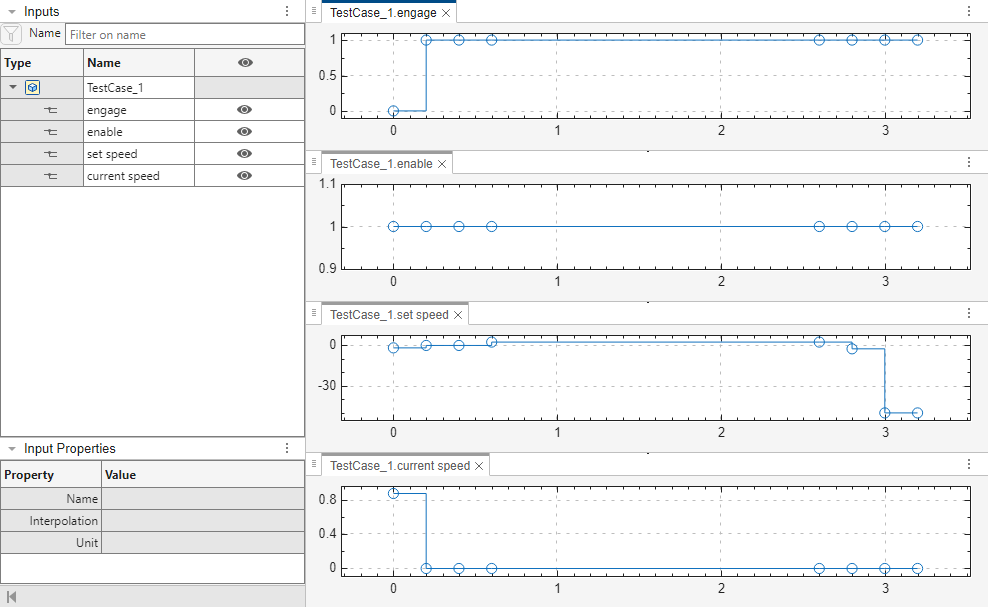

Per visualizzare il caso di test per un obiettivo di coverage del modello, nella finestra Results (Risultati) di Simulink Design Verifier Results, fare clic su View test case (Visualizza caso di test). Si aprono il modello harness sldvexCruiseControl_harness e il blocco Signal Editor.

Il blocco Signal Editor, denominato Inputs, contiene i casi di test. Fare doppio clic sul blocco Inputs per visualizzare il caso di test.

Nota: se si dispone di un modello di grandi dimensioni, l'analisi può produrre un modello harness che contiene un numero elevato di casi di test.

Per generare un numero inferiore di casi di test, impostare il parametro di configurazione del modello Test suite optimization (Ottimizzazione della suite di test) su LongTestcases ed eseguire nuovamente l'analisi.

Quando si imposta Test suite optimization (Ottimizzazione della suite di test) su LongTestcases, l'analisi genera un numero inferiore di casi di test, ma più lunghi, ciascuno dei quali soddisfa più obiettivi di test.

Simulazione di un modello harness e generazione del report sulla coverage del codice

Simulare il modello harness utilizzando i casi di test generati nel modello harness sldvexCruiseControl_harness .

Nel modello harness, fare doppio clic sul blocco Inputs per aprire la finestra di dialogo Block Parameters (Parametri del blocco), quindi fare clic sul pulsante Open Signal Editor (Apri Editor dei segnali) per aprire la finestra Signal Editor (Editor dei segnali).

Nella finestra del modello harness, fare clic su Run all (Esegui tutto).

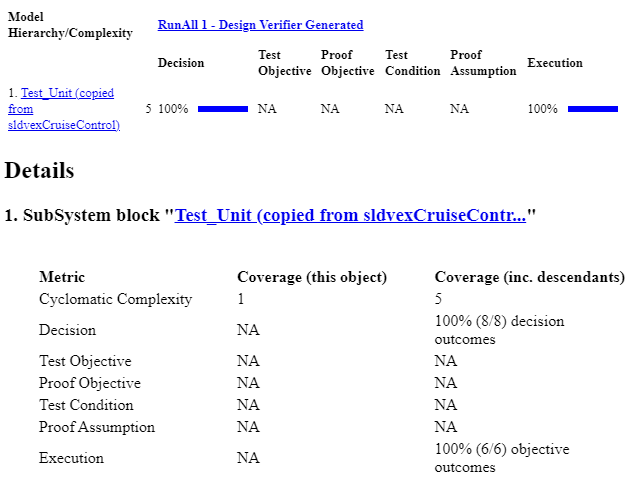

Il software simula il modello harness utilizzando entrambi i casi di test, acquisisce le informazioni sulla coverage del modello e visualizza un report sulla coverage. Il report sulla coverage indica che i casi di test registrano una coverage decisionale del 100% per il modello sldvexCruiseControl.

È anche possibile simulare il modello senza creare un modello harness. Nella finestra di registro di Simulink Design Verifier, fare clic su Simulate tests and produce a model coverage report (Simulare test e generare un report sulla coverage del modello). Per maggiori informazioni sulla coverage del modello, vedere Top-Level Model Coverage Report (Simulink Coverage).

Per maggiori informazioni sul modello harness e sull'utilizzo del blocco Signal Editor per generare un report sulla coverage del modello, vedere Manage Simulink Design Verifier Harness Models.

Visualizzazione del file sldvData

Il file di dati Simulink Design Verifier è un file MAT che contiene una struttura denominata sldvData. Questa struttura memorizza tutti i dati acquisiti e prodotti dall'analisi durante l'analisi stessa. È possibile utilizzare il file di dati per condurre analisi personalizzate o generare report personalizzati.

Per visualizzare il file di dati, fare clic sul nome del file di dati nella finestra di registro che, in questo esempio, è sldvexGenerateTestcasesExample_sldvdata.mat. Quando si fa clic sul nome del file di dati, il software crea una copia dell'oggetto sldvData nel workspace di MATLAB in modo da poter rivedere e manipolare i dati.

Per ulteriori informazioni sui file di dati di Simulink Design Verifier, vedere Manage Simulink Design Verifier Data Files.

Vedi anche

| Simulink Design Verifier Analysis Fundamentals | Check Model Compatibility for Analysis | Highlight Results on the Model