Video Capture USB

Import live video frames from one or more USB cameras on Zynq-based hardware

Since R2024b

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU106

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU102

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

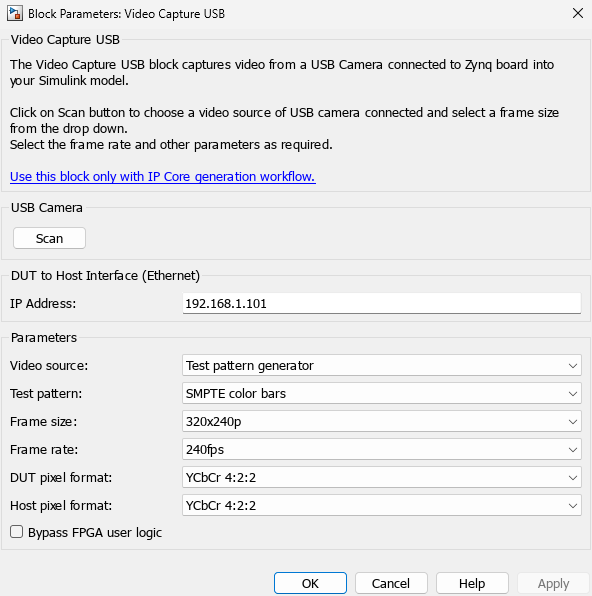

The Video Capture USB block captures video frames from a Zynq®-based board that has one or more USB video device class (UVC) cameras or Basler USB 3.0 cameras, and imports the frames into your Simulink® model. The reference design programs the FPGA with an image that includes a USB camera interface, data path multiplexers, video format conversions, and a video test pattern generator (TPG). You can control these data path and conversion options from the Video Capture USB block.

Examples

Limitations

To use this block, in the hardware setup, set Hardware Board to

Xilinx Zynq UltraScale+ MPSoC ZCU106 Evaluation KitorXilinx Zynq UltraScale+ MPSoC ZCU102 Evaluation Kitand set Add-on Card toUSB Cameras.If you have a Basler USB 3.0 camera, you must download Pylon 6.2.0 Camera Software Suite Linux ARM 64 bit. Download instructions are provided in the hardware setup. If you do not have a Basler USB 3.0 camera, you can click the Skip this step check box on the Pylon® screen in hardware setup.

Capturing data from the USB camera requires certain jumper settings on your board. For details, see Set Jumper Switches.

Use the IP core workflow to generate HDL code. This block does not support using the SoC Builder tool. For more information on workflows, see SoC Generation Workflows.

In the HDL Workflow Advisor tool, in step 1.1, set Target platform to

Xilinx Zynq UltraScale+ MPSoC ZCU106 Evaluation KitorXilinx Zynq UltraScale+ MPSoC ZCU102 Evaluation Kit. In step 1.2, set Reference design toUSB Camera Receive Path.

Ports

Output

Parameters

Version History

Introduced in R2024b