Software-Defined Radio using MATLAB and Simulink

Overview

Wireless engineers can use software-defined radio hardware as a cost-effective, real-time platform for a range of wireless engineering tasks, including over-the-air lab and field testing with live RF signals and rapid prototyping of custom radio functions. Using MATLAB® and Simulink®, users can go from designing and simulating communications algorithms to generating production implementations targeting the Xilinx® Zynq®-7000 All Programmable SoC and Analog Devices AD9361 RF Agile Transceiver.

During our presentation, we will demonstrate how to:

- Model and simulate radio designs

- Verify implementation with radio-in-the loop tests

- Deploy, prototype, and verify custom designs on SDR hardware using HDL and C code generation from algorithm models

About the Presenter

Vidya Viswanathan is an application engineer at MathWorks India specializing in design and implementation of digital signal processing applications. She works closely with customers across domains to help them adopt MATLAB® and Simulink®. Her areas of interest include FPGA and ASIC design, wireless communication, and image processing. Vidya holds a bachelor's degree in electronics and communication engineering from M. S. Ramaiah Institute of Technology and a master's degree in communication and signal processing from Indian Institute of Technology Hyderabad.

Recorded: 24 Sep 2020

Welcome to The MathWorks webinar on software defined radio development using MATLAB and Simulink. My name is Vidya Viswanathan, and I'm an Application Engineer at MathWorks India specializing in wireless design and FPGA implementation. In case you have any questions about the content being presented, I request you to post them in the Q&A window that you see in your WebEx window. We will take a couple of minutes at the end to address these, or we follow up with you on your query.

In case you are facing any issues with the logistics, you can reach out to us in the chat window. During the webinar, there will be a couple of poll questions that will pop up on your screen. I request you to keep a lookout for the poll questions towards the right side of the WebEx window. With this, let's get started with the session.

So what is a software defined radio system? If I had to put it in simple terms, a software defined radio is one in which the physical layer functionality are software defined or software programmed. The programmability of SDRs enable upgradation to the design at any point in time, the addition of new functionalities, as well as the reuse of algorithms.

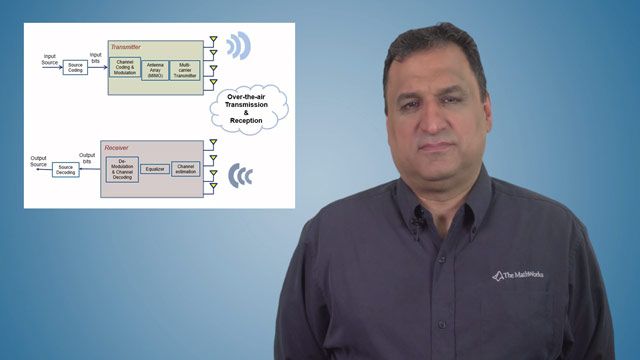

So here is how we view an SDR system. There is an analog front end doing the direct RF conversion with local oscillators and mixers. There are data converters to get the data in and from the digital domain. And you have the digital front end of the SDR, which is responsible for high rate digital signal processing algorithms like digital up-conversion down-conversion, IQ balance, DC offset correction. And then you have the baseband processing with the IQ data amendment.

We think that such a system can be built out of commercial, off-the-shelf hardware. Here's an example of one such system. You have an FMC-based tunable RF card connected to the FPGA evaluation board, which is in turn connected to the desktop computer running an environment like MATLAB or Simulink, using an interface like the Gigabit Ethernet, which you can use to tune RF parameters like the center frequency and RF tilt.

So why is it important to actually look at the implementation workflow for software defined radios because radios have been around for a several number of years now? So in addition to the traditional applications where radios were used, there is a rapid growth in the new application areas of wireless communication. With everything getting connected, even the non-traditional applications, like public safety, surveillance, medical monitoring, agricultural monitoring, smart meters, have started to use cutting edge wireless technology. In addition, the emergence of new wireless standards, like 5G, LTE, and V2X, are enabling this too. However, this requires higher adaptability from the system and a need to quickly design, simulate, and prototype radios. In this regard, software defined radios can be considered as a perfect fit for these applications, yes.

As appealing as the idea of SDRs sound, there are also several challenges involved in developing such system. Given the nature of SDRs, there are a number of different skill sets that are required for creating a robust system, ranging from baseband DSPs, RF and antenna analysis, hardware and software architecture design, FPGA or hardware design, and embedded software development, to name a few. Each of these is a domain by itself, and the skill sets that are required and the design environment that are being used for each are very different. So it is practically difficult for one to be an expert in all of these areas. Therefore, there is a need to have a common design environment that can address multiple domains and also allow the experts in each field to collaborate easy. That is the idea behind this session, to see how MATLAB and Simulink can act as that common development platform.

Before we get started with the work flow, here is an example of how an organization like Orolia used MathWorks' model-based design workflow to develop a receiver for emergency locator beacons. While they have a lot of experience and expertise with respect to the communication system design or the domain, they had limited experience with FPGA design. So they understood that this would actually take a significant amount of the design time, and it would also have an impact on the time that they were able to come up with the first prototype. So with the help of Simulink and HDL Coder, they were able to reduce the FPGA implementation time by 50%, giving them more time for rapid algorithm innovation and technological advancements, while still able to meet their tight deadlines with ease.

So let us look in more detail the workflow that is involved. So you can broadly define the stage of software defined radio development into four aspects. System modeling, that involves the simulation of the entire system to identify the potential design issues only. Once the algorithm has been developed, they can be tested with real signals by integrating MATLAB and Simulink to do the hardware front end. Once you use that to gain the confidence with respect to the algorithm that is developed, the next part of the design process would involve hardware and software development for prototyping and rapid verification with the verification infrastructure or the framework within MATLAB. And the last part of the process would involve the standalone development of the hardware and the integration with the peripherals.

So let's look in a little more detail the first step, that is the modeling and simulation of the entire signal chain, the baseband, the RF front end, as well as the test framework. MATLAB and Simulink provides a wireless designer the ability to model multi-domain system in a single environment, therefore allowing the user to analyze the interrelationship between the different components and how one affects the performance of the other system. You have a host of waveform generation capabilities as well as algorithm development capabilities within MATLAB and Simulink in the form of library functions as well as blocksets.

You can design and architect your RF front end and include the effects of nonlinearities in your system. You can also design your data converters, like the analog to digital converters or the DACs, and finally integrate the sim with the effects of antenna as well as the propagation channel. So MATLAB provides a rich set of library functions and graphical user interface to generate the standard compliant waveforms for different wireless standards, like 5G, LTE, WLAN, Zigbee, NFC, as well as Bluetooth Low Energy. You can also reuse this framework to design custom waveforms and provide parameterizations for them.

The processing ability within MATLAB and Simulink also enable you to do the complete physical layer development starting from the waveforms generation, including the effects of channel and the RF impairment and design of a practical receiver. There are several set of examples for the end-to-end link level simulation for standard as well as non-standard-based wireless systems that you can use as a starting point for your algorithm development. These are all available in the form of MATLAB code and Simulink models that you can easily configure and modify based on the system that you are making.

The fidelity of the system or the end-to-end simulation, link level simulation that you have created can be further improved by integrating the physical layer design with the behavioral aspects of RF front end. The introduction of the RF front end models enables the user to develop more practical and robust receivers. The RF front end is simulated through RF blockset, and you can use this framework to perform a closed loop simulation of the baseband with the RF front end by integrating MATLAB and Simulink and running the complete chip.

There is also a set of modules that are available and Simulink models available for commercial, off-the-shelf RF front end transceivers, like the analog devices AD9361 and AD9371 transceiver. These behavioral models have been tested against the actual hardware setup in a lab kind of an environment, and we have been able to correlate the results between the simulation model and the hardware model. Therefore, if you're working on SDR platforms which involve these RF transceivers, you can directly plug in these models into your baseband algorithm.

There are also a number of reference examples that show how you can connect your baseband processing with the transceiver models. Let's look at an example now. I have here a QPSK-based transmitter where the baseband algorithm is defined in Simulink, which is connected to the transmitter model of my AD9361. Then there is a channel representation which is also in turn connected to the AD9361 receiver, and the algorithm for the demodulation happens there. And you're seeing the constellation as well as the error rate estimation.

So a closer look at the AD9361 receiver architecture actually gives you the insight that this particular model actually has the complete architecture of the transceiver model, including the RF front end, the series of analog as well as digital filters, and the analog to digital converter, and the AGC that is present in the AD9361 transceiver. If you're interested, you can download these models of the RF transceivers in the link that you see on the screen. In case you're working on custom RF front end design, there are multiple examples that show you how you can simulate the practical radio with the RF transmitter and receiver models, and again, these examples range between LTE, WLAN, 5G, as well as non-standard protocol-based radios as well.

So let's move to the next part of the SDR design, which is validation of the algorithm with streaming RF data. So here, what we see is the baseband processing and the test infrastructure is still with within MATLAB and Simulink environment. However, the data that I'm actually feeding to test my baseband processing is coming from a real life scenario.

So you can connect MATLAB to several RF instruments and SDR platforms directly for over DL testing of the radio with real signals. You can get a near real time streaming of the RF data into MATLAB, and the reason I say near real time is because you would be limited by the interface transfer rate and the host computer's performance. But you can bring in a continuous burst of data and then use that for further algorithm design or downstream analysis. So this helps you validate your design even before you start looking into the hardware and the software aspects of the design. And this is enabled through system objects and blocks that help you connect easily to different SDR platforms and also tune the radio parameters.

Let's see an example of how an FM broadcast signal can actually be captured by an SDR platform and brought into MATLAB. So the first step would involve configuring or connecting to the radio hardware. So you have a function to connect to the hardware. You can then start configuring certain parameters, like the center frequency, the baseband sample rate, as well as the data type of the samples that you're receiving, and then use the captured function to actually record the data into either a file or into a variable in the MATLAB work space.

So what I'm doing in this case is I created a file where I captured the FM signal. Once I have that file present, I can import that into MATLAB using the baseband file reader. And then once it is brought into MATLAB environment, you can use this for doing any kind of analysis, or you can also pass it to your receiver.

So here, I created a spectrum analyzer, and I'm actually going to look at the frequency of the received captured FM bank. So you can see in this view that there is a spectral view as well as a spectrogram that you're observing with respect to this signal. The same thing can be replicated for an LTE signal which you can capture from the real scenario into MATLAB environment and perform the cell search.

So again, similar to what we saw previously, I'm first connecting to the radio object. Then I'm using the Capture function to get the received waveforms, and I'm collecting it for a couple of seconds. And then I'm actually using the functions with an LTE tool box to actually do the cell search and figure out what is the cell ID of the signal. So you can see that the detected cell ID or the recorded cell ID actually matches what I was expecting or what I was looking at receiving. So this helps you validate if the algorithm that you developed is robust enough and whether any further modifications are required to be able to adapt to the real impairments that are introduced by the cell.

So let's actually see what are the different SDR platforms that are actually supported for this radio streaming as well as capturing of RF signals within MATLAB environment. You can see the list of the SDR platforms here. If you're also interested in understanding more on the specifics of these configurations, I would request you to actually click on the link, which contains the link to the support package.

All right, so now, we have looked at two different aspects with respect to SDR design. One was the compute system modeling and the second one was algorithm and validation with real life signals. So let's move to the next aspect of the SDR development, which basically involves partitioning your algorithm into hardware and software components and then start prototyping on the implementation platform, which could be either an FPGA, or it could be a system-on-chip platform.

So this involves the design of RDL code for targeting your FPGAs, as well as C code for targeting the processor and to be able to communicate between these two as well as with the RF front end, to do a complete implementation or prototyping on any of these standard development ports. So if you actually look at the wireless reference algorithms that we were developing up to this point, the frameworks that we used for the development of these reference algorithms are quite different from what a hardware implementation engineer would actually be looking at. So what I mean is that if you consider the wireless reference algorithms that we were previously building, it was mostly working on a vector of data or a frame of data. We assumed that we had a compute chunk of data available with us. And most of the operations that we were performing were on floating point precision.

Whereas if you look at the hardware implementation side, it is important to understand how you're going to be working with streaming bits as the data samples keep coming in and also how you can work with fixed point architecture. So there is a disconnect between these two aspects, and what we will be looking at is to figure out a way to actually smoothen this transition from the wireless reference algorithm to the hardware implementation. So this would involve a couple of intermediate steps, which is what we're going to be looking at in a little more details.

So if you actually look at the workflow that is involved with respect to the wireless algorithm design, you can-- the first step would involve categorizing the whole aspect into three different parts. The first would be the stimuli. The second would be the reference algorithm. And the third part will be whatever verification or analysis that you want to do with the results. So I can write a test script, or I can use the existing examples within the MATLAB framework to create different kinds of waveforms that I feed into my reference algorithm. And then I can use again the MATLAB environment for either visualizations, or I can use that to get the error matrices.

So now, the important aspect that would come into picture to make this a little more representative of what actually gets implemented on the hardware is to translate this reference algorithm into a sample-based or a stream-based process. This is where we make use of a combination of MATLAB as well as the Simulink environment. MATLAB, being more script-based, is well suited to work with large matrices of data. And Simulink, since it works on the basis of a software and has the notion of time built in it, it can be used to better represent the sample-based process.

So we are going to be looking at translating the reference algorithms into the sample-based processing and start bringing in the streaming nature and modify the algorithms accordingly. So another important aspect, when you're working with the streaming data, is to be able to figure out at what point you're actually starting the ballot samples, and at what point you're ending the data, and in the middle of all of these, how many of those have been valid samples. So we can create those control signals, which will also help you with the comparison against the MATLAB golden reference.

So once I have architected my model in such a way that it actually considers some of the hardware aspects in the picture, the next step that is involved is the fixed point quantization. MATLAB and Simulink allows you to modify the data types of your signals from floating point, which is the default data type, into fixed point representation, which is suited for the hardware architecture that you're looking at. It's important to choose the right set of fixed point data types because this not only controls the accuracy of your algorithm, but it also controls the amount of resources that it's going to occupy on your FPGA platform. With the help of Fixed-Point Designer, you can convert the MATLAB and Simulink floating point algorithms into an equivalent fixed point representation. And at each stage, you can compare it against the golden reference that you're starting with to see what is the amount of quantization introduced and whether that is within the error tolerance that you're looking for.

So with respect to wireless design, one of the ways in which we have tried to ease this process of transitioning your reference algorithms into a hardware-friendly version is by the introduction of the Wireless HDL Toolbox, which basically consists of hardware IPs for streaming-based wireless design, which works in such a way that they're very friendly on the FPGA architecture. And we also have a set of reference applications that you can use as a starting point for different standards, 5G, LTE, WLAN, or any custom configuration. And you can create your reference Simulink model using the blocks within the Wireless HDL Toolbox. And the advantage of that is once you have created this system and compared it against your initial reference, you can use code generation techniques to actually generate the synthesizable open RTL code from within this environment.

So just like how we have looked at the elaboration with respect to the FPGA aspect, Simulink can also be used to represent the software aspect. So if you actually look at the model, and I'm just simplifying it into two aspects, algorithm one is what is going to be targeted on the FPGA. And algorithm two is what is going to be on the processor.

So from this model, with the help of HDL Coder and Embedded Coder, I can generate the corresponding programming language, the HDL Verilog in case of HDL Coder and CC++ code in case of Embedded Coder. And if you actually look at this representation, this is a form where we have translated the algorithm which was at the high level representation like Simulink into a code which is one step towards hardware implementation. But if you look at the ultimate hardware platform that you're going to be running this, there is another important aspect that actually comes into picture, in addition to just the FPGA and the processor aspects, which is the interconnects between these two and the peripherals.

So the effect that these interconnects can have is pretty significant on the algorithm design. So although there is a direct transition from the algorithm model to the algorithm code, this code may or may not work directly when just directly plugged into the hardware environment because of some of the effects of these interconnects. So the idea is to bridge this gap of transitioning from this algorithm model into a more closer representation of what my hardware platform would look like, and that is primarily what we're going to be looking at in the next aspect.

In addition to your FPGA algorithm and your processor algorithm, Simulink allows you to also simulate the interconnects between the FPGA and the processor. So if it is interacting with an external memory environment, what are the latencies that are introduced in that case? If you're working with AXI-based registers, again, what are the different configurations with respect to that? What are the I/Os that the FPGA and the processor are interacting with? All these aspects can actually be simulated first, along with your algorithm. This gives you a more realistic view of what you're going to expect from your hardware, and this is enabled to SoC blockset.

The different steps that are involved in this process would be simulation of the hardware architecture, along with the algorithms, then deploy it on the prototyping FPGA or SoC platforms. And the third step that can also be done is to profile the results from the hardware and bring it back into the MATLAB simulated environment to actually understand what was the effect of the OS or whether there was actually real stream detail of the input, output samples and how much was the core algorithm actually utilizing in terms of the resources. So if you've been able to simulate this entire system, and then if you go in for the code generation process, you can be a little more assured that what you can expect out of the hardware, you've actually identified some of those potential issues and corrected those in the algorithm.

So the next aspect would be to come up with a standalone implementation of this review, where you're not only taking into consideration the algorithm aspects, but also the interconnects. And this is enabled through reference designs. So let's actually look at an example of how such a system and be developed, by looking at a simple model.

The example that I'm considering here is a 5G cell search reference application. So you can see that one important aspect would be to create the 5G reference waveform, which you can easily do with the help of 5G Toolbox. Then you would have to define or architect your cell search algorithm which is going to be running on your own hardware, and there could be certain portions which would run on your software.

So in this case, I have a search control algorithm which I'm running on my software, which helps me choose the strongest SS block and also correct for the frequency offset and help determine the cell ID. So the software component actually provides as an input to the FPGA, the frequency offset as well as the subcarrier spacing. And decoding of the demodulation to actually find out the SSS, PSS, as well as the cell ID, is actually implemented in the hardware aspect, which is the FPGA code.

So like I mentioned previously, you can use the reference example within the Wireless HDL Toolbox, which consists of a Simulink model that actually does the complete cell search. This Simulink model can be tested with the data stimulus from the MATLAB environment. So you can create a series of test waveforms using 5G Toolbox, feed that into the Simulink model, and do a comparison of the results that you are getting from the MATLAB golden reference as well as the Simulink model. And the reason this step is important is you can actually see what is now the effect of the latency as well as the quantization that your fixed point architecture is going to bring into picture. And there are a whole set of intermediate signals that you can actually tap, and you can do the edit analysis or the comparison between these.

So once you have tested this particular algorithm with the simulated set of data, the next step that is involved is to include the simulation of the architecture aspects, and if possible, bring in the capture of the RF signal from the livestream. So what we see here is a model of the NR cell search algorithm, where the same FPGA logic consists of the receiver algorithm. I'm also having the processor module, the memory interface simulator, as well as the RF data converter. So this is representative of a Xilinx RFSoC architecture.

So if you actually take a closer look at the FPGA part of the subsystem, you can see the Simulink model for the cell search receiver, and you can observe that this is a model completely using fixed point representation. And this basically gives out the cell ID that you're detecting. So this the processor part of the model, which consists of a task manager as well as the ability to send the data into the host computer. So now, I can simulate this entire system, which is basically consisting of captured RF data and the algorithm, to see at what point the PSS is found or the SSS demodulation is done. And this also includes, in addition to just the algorithm aspect, some of the latencies that are introduced because of the memory interfaces that are also being used.

So now, I've kind of simulated the entire system and gotten confidence with respect to the complete development of what I can expect from my hardware environment. So the next aspect involved in this process would be to implement this on the hardware. You can target different FPGA and SoC platforms with the help of the reference designs that we provide in the hardware support package.

You can see the two links on the screen here. This consists of the reference design for a different set of hardware, and this basically helps you then pick not only the algorithm code that you generate from the code products but also integrated with the rest of the design, and you generate a bit stream for the particular hardware that you're looking at. In this example, I've actually programmed the RFSoC by connecting to this front end Simulink model and directly running the hardware as well as the software aspects on the RFSoC hardware.

I can also use this to actually plot certain signals and actually understand the hardware state for the PSS search and demodulation. So this is data from the hardware that I'm probing back. And you can also see that the processor sends in the decoded cell ID as well as the PSS and SSS SNR values, which I'm visualizing back within the MATLAB environment by using the UDP Receive block. This helps you with the complete prototyping and development framework with respect to SDR platforms. I have taken as an example RFSoC, but like I mentioned previously, there are a whole set of hardware that we support in this workflow.

So before we look into the different platforms that are supported, I also wanted to bring your notice to another customer success story. RF Pixels used this particular workflow for targeting their LTE reference algorithms on the Zynq RFSoC hardware. Again, with the help of HDL Coder, they were able to reduce the time to actually come up with the first prototype, and they were able to do the iterations of the design much more easily and quickly, thereby reducing the iteration times from weeks to days. There is also a link to this particular article. If you're interested in knowing a little more details about how they used this workflow, you can look at that.

So here is a snapshot of the different SDR platforms that we support for targeting. When I say these are the supported platforms for targeting, what I mean is that in addition to the algorithm code, for these particular hardware platforms, we have the reference design available. However, you can also use the generated code. And if you can create or integrate with a custom reference design, you can also reuse this framework for targeting custom SDR platforms as well.

To get started with respect to the SDR development, we, again, have a number of reference applications that we have put together. Depending on the scale of the system, these can be implemented on different hardware environment. So you'll see a whole set of 5G, or LTE, or QPSK-based system that are being modeled and tested on either RFSoC or the Zynq-based SDR system.

If I had to summarize, we have seen in this particular session how much MATLAB and Simulink can act as this unified platform for wireless development, which involves the design of the algorithm, which will be the baseband, RF front end, antenna, and the channel effects. You can then validate this algorithm by connecting to real instruments or the RF test instruments and SDR platforms, through the integrated workflow that we have and the support that we have to connect to these hardware. And once you have validated your algorithm, you can then use the code generation technology to actually target the algorithms that you have developed onto FPGA, or a processor, or a system-on-chip environment.

So if you're interested in knowing a little more about the model-based design workflow that I covered for a software defined radio development, you can actually visit the SDR page within the MathWorks website. This has a set of white papers, videos, as well as reference examples that you can use to get started with this workflow, and it will cover all the aspects that you just looked at in this webinar. If you're working with RFSoC development board, we have a dedicated page to actually talk about the way in which we support RFSoC platforms. So again, the link of that is provided, and we can see what are the reference examples that are available in this and also what kind of support we offer with respect to the RFSoC targeting.

And if you want to get a more hands-on experience with this particular workflow, we have a range of training that we offer. These are hands-on training which ranges from the wireless communication algorithm design, or it could be on the HDL code generation part, or it could be on the software development or the customization of the Linux OS or this complete software defined radio on Zynq platforms that we just looked at. And if you're interested in customizing these training courses as per your needs to make it more suited for the requirements that you are working on, I would encourage you to contact the training services team within MathWorks, and the link is provided there to reach out to them.