FPGA HDL Code Generation

Models or subsystems with fast sample time requirements may benefit from FPGA simulation. If you have HDL Coder™, you can convert your Simscape plant model to an HDL implementation model that you can then use to generate HDL code to deploy to an FPGA. To deploy your Simscape model or subsystem to an FPGA:

Use the

sschdladvisorfunction to launch the Simscape HDL Workflow Advisor, which guides you through the process of creating the HDL implementation model.Convert the implementation model to HDL code using the HDL Workflow Advisor tool.

Use Simulink® Real-Time™ to deploy the HDL code to a FPGA.

You can use model synthesis to predict the achievable hardware time step.

Functions

sschdladvisor | Open Simscape HDL Workflow Advisor |

simscape.findNonlinearBlocks | Check model for blocks with nonlinear equations |

sschdl.updateRuntimeParameters | Generate updated tunable parameter data file for Simscape model (Since R2024a) |

sschdl.generateOptimizedModel | Replace Simscape switches and converter blocks with dynamic switches optimized for FPGA deployment (Since R2024a) |

Topics

- Get Started with Simscape Hardware-in-the-Loop Workflow (HDL Coder)

Simscape™ Hardware-in-the-Loop workflow modeling guidelines and restrictions.

- Linearize a Simscape Model to Prepare for HDL Code Generation

Learn how to linearize a model that uses the Backward Euler solver for HDL deployment.

- Generate HDL Code for FPGA Platforms from Simscape Models

Learn how to convert Simscape models to HDL Code for FPGA Deployment.

- Generate Optimized HDL Implementation Model from Simscape (HDL Coder)

Optimize area and timing of HDL implementation model generated from Simscape by using HDL Coder optimizations.

- Generate and Validate HDL Code for Simscape Model (HDL Coder)

Generate HDL code from Simscape switched linear models.

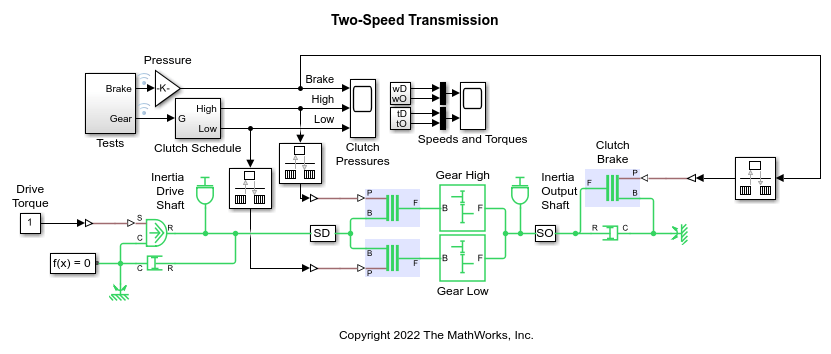

- Generate HDL Code for Simscape Models with Multiple Networks (HDL Coder)

Split a large Simscape network into multiple networks and generate HDL implementation model.

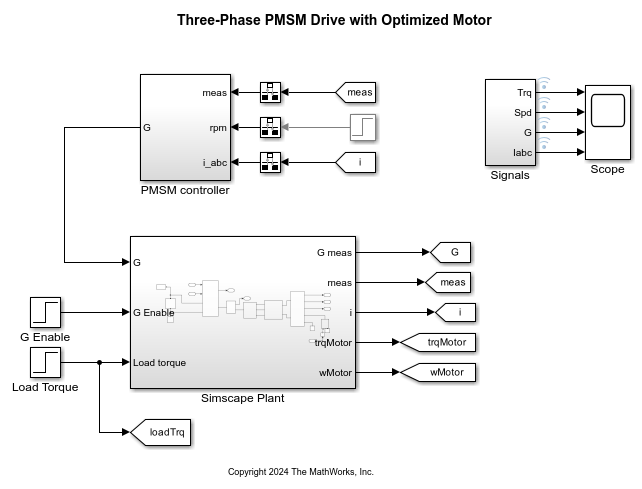

- Generate HDL Code for Simscape Three-Phase PMSM Drive Containing Averaged Switch (HDL Coder)

Generate HDL code and synthesize the results for a three-phase PMSM Simscape models with converter blocks that have averaged switches and deploy onto the FPGAs.

- Simulate Large Time Steps Using Trapezoidal Rule Solver for Real-Time FPGA Deployment (HDL Coder)

Generate HDL code for a Simscape model by using the Trapezoidal Rule solver and deploy it onto a Speedgoat® FPGA I/O module.

- Generate HDL Code for Simscape Models by Using Dynamic Switch Approximation (HDL Coder)

Generate HDL code and synthesize the results for a three-phase PMSM drive using Dynamic Switch Approximation method.

- Improve FPGA Sampling Frequency of HDL Implementation Model Generated from Simscape Algorithm (HDL Coder)

Oversampling in generated HDL implementation model, and relation between model sample time and sample time of original Simscape algorithm.

- Validate HDL Implementation Model to Simscape Algorithm (HDL Coder)

Validate and resolve simulation mismatch between Simscape algorithm and HDL implementation model.

- Synthesis Results for Simscape Hardware-in-the-Loop Workflow (HDL Coder)

Access synthesis results for Simscape hardware-in-the-loop workflow example models.

Troubleshooting

Resolving Issues with Nonlinearities

Troubleshoot simulation and code generation issues associated with nonlinearities.

Troubleshooting Real-Time Hardware Deployment Issues in Simscape Hardware-in-the-Loop Workflow (HDL Coder)

Troubleshoot real-time hardware deployment issues in Simscape Hardware-in-the-Loop workflow.

Troubleshoot Validation Errors in Simscape Hardware-in-the-Loop Workflow (HDL Coder)

Troubleshoot validation mismatches in Simscape Hardware-in-the-Loop workflow.